# **DDR5 Client VR on DIMM PMIC**

## 1 Features

- VIN\_Bulk Input Supply Range: 4.25V to 5.5V

- Three Buck Converters: SWA, SWB & SWC

- Configurable Dual Phase and Single

Phase Node for SWA and SWB

- 0.75% Output Accuracy

- Configurable Switching Frequency of

Buck

- CCS COT Mode Enables Fast Transient Response

- 2 LDO Regulators: VOUT\_1.8V, VOUT\_1.0V

- Secure Mode and Programmable Mode

of Operation

- Supports I<sup>2</sup>C and I<sup>3</sup>C Interface

- Controllable Soft-start /Soft-stop Time of

Buck

- Protection Functions, Including OVP, UVP, OCP and OTP

- Power Good Indicator

- General Status Interrupt Function

- WQFN-28 Package

- RoHS Compliant

## 2 Applications

DDR5 SO-DIMM, UDIMM

## **3** Description

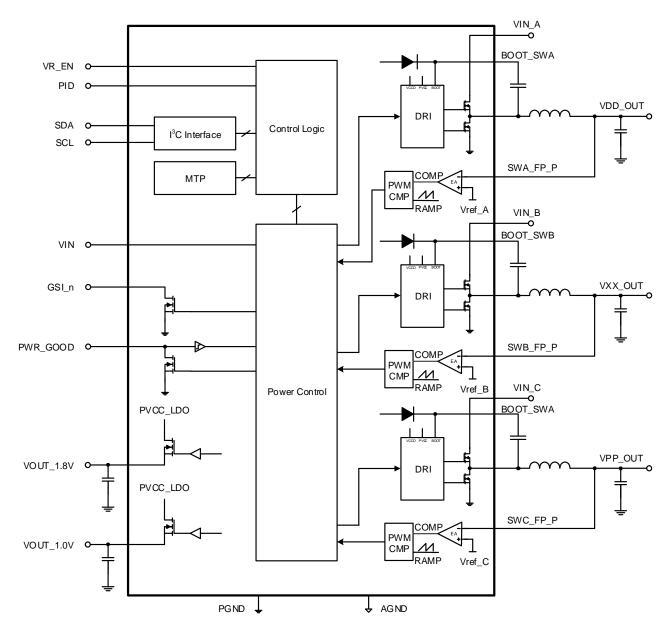

The GD30MP1000 is an integrated solution for DDR5 SODIMM and UDIMM power management IC. The PMIC features three buck converters and two LDO regulators. The buck converters are designed by capacitor current sense constant on time (CCS COT) control that provides fast transient response, the noise immunity and all kinds of very low ESR output capacitor for ensuring performance stabilization. All three buck converters equip with automatic power saving mode (PSM) for optimizing efficiency. The two LDO regulators, VOUT\_1.0V and VOUT\_1.8V, can supply DIMM module's sideband and SDP usage. The PMIC supports selectable interface (I2C or I3C Basic) to fit various application environment.

Two of the buck converters (SWA and SWB) can be configured to operate in dual-phase single channel. Two ADCs are implemented to monitor the current consumptions of the buck converters and the voltage information of the input/output rails.

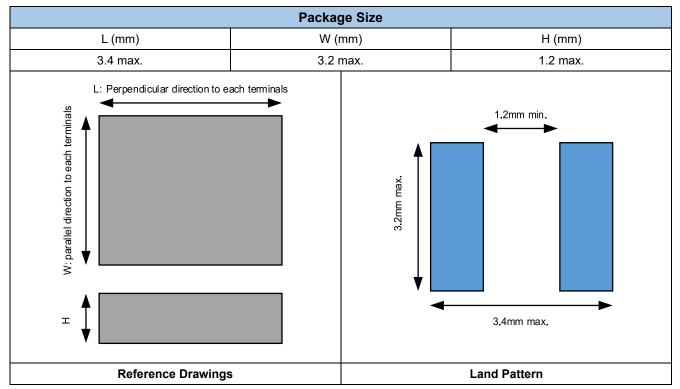

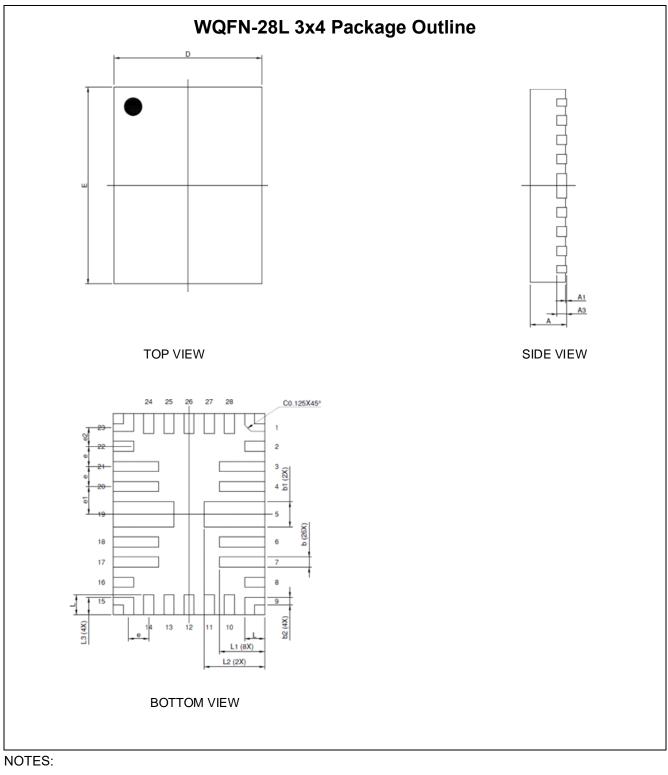

The GD30MP1000 is available in low-profile thermal enhanced WQFN-28 (3.00 mmx4.00 mm) package.

#### **Device Information<sup>1</sup>**

| PART NUMBER | PACKAGE  | BODY SIZE (NOM)   |

|-------------|----------|-------------------|

| GD30MP1000  | WQFN-28L | 3.00 mm x 4.00 mm |

1. For packaging details, see *Package Information* section.

## **Table of Contents**

| 1   | Featu   | res                              | 1    |

|-----|---------|----------------------------------|------|

| 2   | Appli   | cations                          | 1    |

| 3   | Desci   | iption                           | 1    |

| Tab | le of C | ontents                          | 2    |

| 4   | Devic   | e Overview                       | 3    |

|     | 4.1     | Pinout and Pin Assignment        | 3    |

|     | 4.2     | Pin Description                  | 3    |

| 5   | Paran   | neter Information                | 6    |

|     | 5.1     | Absolute Maximum Ratings         | 6    |

|     | 5.2     | Recommended Operation Conditions | 6    |

|     | 5.3     | Electrical Sensitivity           | 6    |

|     | 5.4     | Thermal Resistance               | 6    |

|     | 5.5     | Electrical Characteristics       | 7    |

| 6   | Funct   | ional Description                | 11   |

|     | 6.1     | Block Diagram                    | . 11 |

|     | 6.2     | Operation                        | .12  |

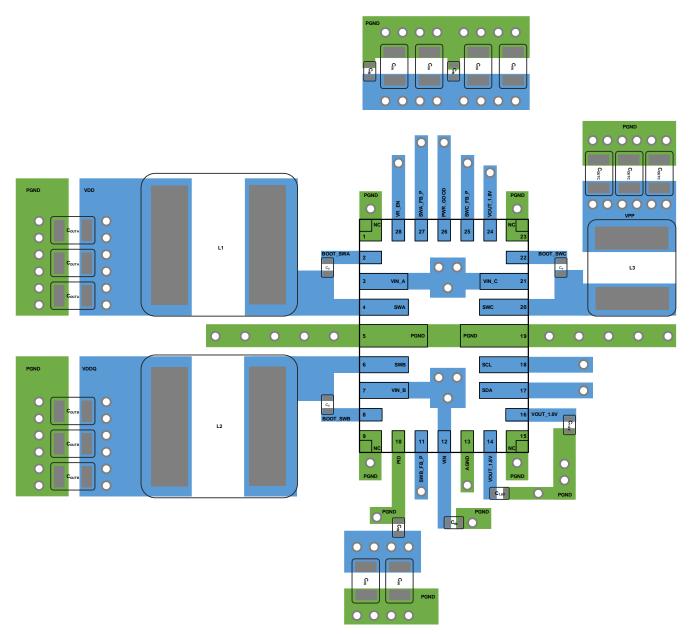

| 7   | Appli   | cation Information               | 28   |

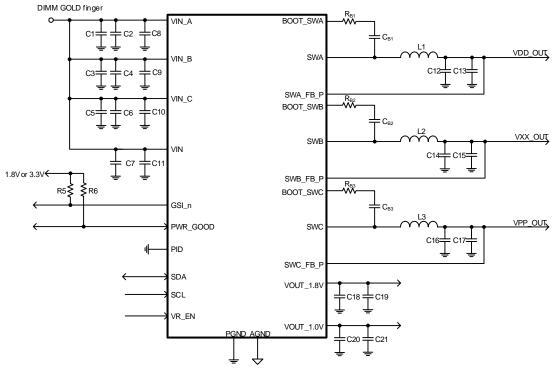

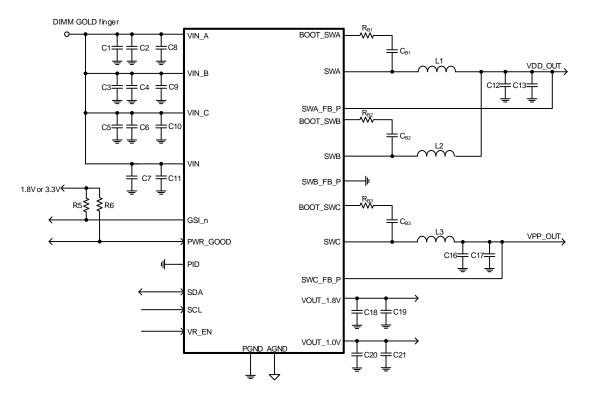

|     | 7.1     | Typical Application Circuit      | .28  |

|     | 7.2     | Detailed Design Description      | .29  |

| 8   | Regis   | ter Description                  | 34   |

|     | 8.1     | Register Attribute Definition    | .34  |

|     | 8.2     | Register Map Breakdown           | .34  |

|     | 8.3     | Host Region Register Map         | .34  |

|     | 8.4     | DIMM Region Register Map         | .39  |

|     | 8.5     | Register Definition              | .41  |

| 9   | Layou   | It Guidelines and Example        | 83   |

| 10  | Packa   | age Information                  | 85   |

|     | 10.1    | Outline Dimensions               | .85  |

| 11  | Order   | ing information                  | 87   |

| 12  | Revis   | ion History                      | 88   |

## 4 Device Overview

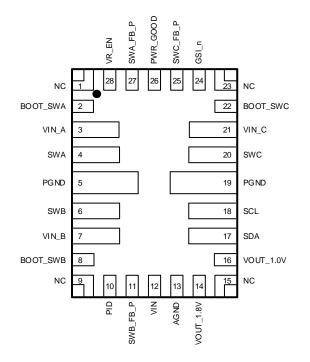

## 4.1 Pinout and Pin Assignment

## 4.2 Pin Description

| P        | IN           |   | FUNCTION                                                               |

|----------|--------------|---|------------------------------------------------------------------------|

| NAME     | NO           |   | FUNCTION                                                               |

| NC       | 1, 9, 15, 23 |   | Non-functional pins. No internal connections to the chip.              |

|          |              |   | Buck A bootstrap. Bootstrap node for switch node SWA high-side         |

| BOOT_SWA | 2            | 0 | NMOS driver. Connect a capacitor between SWA and BOOT_SWA to           |

|          |              |   | form a floating supply across the high-side switch driver of Buck A.   |

| VIN_A    |              |   | 5V power input supply to the PMIC for SWA, SWB and SWC                 |

| —        | 3, 7, 21     | Ρ | respectively. All three VIN_Bulk input pins must be connected to the 5 |

|          | 3, 7, 21     |   | V input supply even if one or more output regulators are not intended  |

|          |              |   | to be used.                                                            |

|          |              |   | Switch node A output buck regulator. This pin connects to L1 power     |

|          |              |   | inductor.                                                              |

|          |              |   | In single phase regulator mode of operation, the SWA output must not   |

| SWA      | 4            | Р | be connected to SWB output even if they are configured to same         |

|          |              |   | exact output voltage.                                                  |

|          |              |   | In dual phase regulator mode of operation, the SWA and SWB             |

|          |              |   | outputs are connected.                                                 |

| PGND     | 5, 19        | G | Power Ground. Connect PGND to DIMM ground plane.                       |

| P         | IN |                       |                                                                                                                                                                                                                                                                                                                                            |

|-----------|----|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME      | NO | PIN TYPE <sup>1</sup> | FUNCTION                                                                                                                                                                                                                                                                                                                                   |

| SWB       | 6  | Ρ                     | Switch node B output buck regulator. This pin connects to L2 power<br>inductor.<br>In single phase regulator mode of operation, the SWB output must<br>not be connected to SWA output even if they are configured to same<br>exact output voltage.<br>In dual phase regulator mode of operation, the SWA and SWB<br>outputs are connected. |

| BOOT_SWB  | 8  | 0                     | Buck B bootstrap. Bootstrap node for switch node SWB high-side<br>NMOS driver. Connect a capacitor between SWB and BOOT_SWB to<br>form a floating supply across the high-side switch driver of Buck B.                                                                                                                                     |

| PID       | 10 | I                     | PMIC ID pin for I <sup>2</sup> C and I <sup>3</sup> C Basic bus.                                                                                                                                                                                                                                                                           |

| SWB_FB_P  | 11 | I                     | Switch node B output buck regulator positive feedback. In single<br>phase regulator mode of operation, this pin connects to DIMM power<br>plane load. In dual phase regulator mode of operation, this pin is<br>connected to GND.                                                                                                          |

| VIN       | 12 | Р                     | 5 V power input supply to the PMIC for analog circuits.                                                                                                                                                                                                                                                                                    |

| AGND      | 13 | G                     | Analog Ground. Connect AGND to DIMM ground plane.                                                                                                                                                                                                                                                                                          |

| VLDO_1.8V | 14 | Р                     | 1.8V LDO Output.                                                                                                                                                                                                                                                                                                                           |

| VLDO_1.0V | 16 | Р                     | 1.0V LDO Output.                                                                                                                                                                                                                                                                                                                           |

| SDA       | 17 | IO                    | Data input and output for I <sup>2</sup> C and I <sup>3</sup> C Basic bus management interface.                                                                                                                                                                                                                                            |

| SCL       | 18 | IO                    | Clock input for I <sup>2</sup> C and I <sup>3</sup> C Basic bus management interface.                                                                                                                                                                                                                                                      |

| SWC       | 20 | Р                     | Switch node C output buck regulator. This pin connects to L3 power inductor.                                                                                                                                                                                                                                                               |

| BOOT_SWC  | 22 | 0                     | Buck C bootstrap. Bootstrap node for switch node SWC high-side<br>NMOS driver. Connect a capacitor between SWC and BOOT_SWC to<br>form a floating supply across the high-side switch driver of Buck C.                                                                                                                                     |

| GSI_n     | 24 | 0                     | General Status Interrupt. Open Drain Output. This PMIC asserts this<br>pin low to communicate any or more events to host. This pin stays<br>asserted until the appropriate registers are explicitly cleared and<br>event is no longer present.                                                                                             |

| SWC_FB_P  | 25 | Р                     | Switch node C output buck regulator positive feedback. This pin connects to DIMM power plane load.                                                                                                                                                                                                                                         |

| P         | N  |                       | EUNICTION                                                              |

|-----------|----|-----------------------|------------------------------------------------------------------------|

| NAME      | NO | PIN TYPE <sup>1</sup> | FUNCTION                                                               |

|           |    |                       | Power good indicator. Open Drain output. The PMIC floats this pin      |

|           |    |                       | high when VIN_Bulk input supply as well as all enabled output buck     |

|           |    |                       | regulators and all LDO regulator tolerance threshold is maintained as  |

|           | 26 |                       | configured in appropriate register. The PMIC drives this pin low when  |

| PWR GOOD  |    | 0                     | VIN_Bulk input goes below the threshold or when any of the enabled     |

| TWIC_GOOD |    |                       | switch output regulators exceeds the threshold configured in the       |

|           |    |                       | appropriate register or any LDO output regulator exceeds the           |

|           |    |                       | threshold tolerance.                                                   |

|           |    |                       | Input: The PMIC disables its output regulators when this pin is low.   |

|           |    |                       | The LDO outputs shall remain on.                                       |

|           |    |                       | Switch node A output buck regulator positive feedback. In single       |

| SWA_FB_P  | 27 | Р                     | phase or dual phase regulator mode of operation, this pin connects to  |

|           |    |                       | DIMM power plane load.                                                 |

|           |    |                       | PMIC Enable. When this pin is high, the PMIC turns on the regulator.   |

| VR_EN     | 28 | I                     | When this pin is low, the PMIC turns off the regulator. This pin shall |

|           |    |                       | not be left floating. If it is not used, it shall be tied to GND.      |

1. I = Input, O = Output, IO = Input/Output, P = Power, G = Ground.

## 5 Parameter Information

### 5.1 Absolute Maximum Ratings

The maximum ratings are the limits to which the device can be subjected without permanently damaging the device. Note that the device is not guaranteed to operate properly at the maximum ratings. Exposure to the absolute maximum rating conditions for extended periods may affect device reliability.

| SYMBOL                | PARAMETER                                         | MIN  | MAX | UNIT |

|-----------------------|---------------------------------------------------|------|-----|------|

| VIN, VINA, VINB, VINC | Supply Input Voltage                              | -0.3 | 6.0 | V    |

| AGND to PGND          |                                                   | -0.3 | 0.3 | V    |

| Other I/O             |                                                   | -0.3 | 6.0 | V    |

|                       | DC                                                | -0.3 | 6   | V    |

| SWA, SWB, SWC         | <25ns Transient                                   | -0.3 | 9   | V    |

| TJ                    | Operating junction temperature                    | -40  | 155 | °C   |

| T <sub>stg</sub>      | Storage temperature                               | -55  | 150 | °C   |

| P <sub>max</sub>      | Maximum power dissipation @ T <sub>A</sub> =+25°C |      | TBD |      |

#### 5.2 **Recommended Operation Conditions**

| SYMBOL <sup>1,2</sup> | PARAMETER                      | MIN  | ТҮР | MAX | UNIT |

|-----------------------|--------------------------------|------|-----|-----|------|

| VIN, VINA, VINB, VINC | Supply Input voltage           | 4.25 |     | 5.5 | V    |

| T <sub>A</sub>        | Operating ambient temperature  | 0    |     | 85  | °C   |

| TJ                    | Operating junction temperature | -10  |     | 125 | °C   |

1. The device is not guaranteed to function outside of its operating conditions.

### 5.3 Electrical Sensitivity

| SYMBOL    | CONDITIONS                                                          | VALUE | UNIT |

|-----------|---------------------------------------------------------------------|-------|------|

| Vesd(HBM) | Human-body model (HBM), ANSI/ESDA/JEDEC JS-001-2017 <sup>1</sup>    | 2000  | V    |

| Vesd(CDM) | Charge-device model (CDM), ANSI/ESDA/JEDEC JS-002-2022 <sup>2</sup> | 500   | V    |

1. JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

2. JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### 5.4 Thermal Resistance

| SYMBOL <sup>1</sup> | CONDITIONS                   | PACKAGE | VALUE | UNIT |

|---------------------|------------------------------|---------|-------|------|

| ΘJA                 | Natural convection, 2S2P PCB | WQFN28  | TBD   | °C/W |

| Θ」C                 | Cold plate, 2S2P PCB         | WQFN28  | TBD   | °C/W |

1. Thermal characteristics are based on simulation, and meet JEDEC document JESD51-7.

### 5.5 Electrical Characteristics

Limits apply over the full operating ambient temperature range ( $0^{\circ}C \le T_A \le +85^{\circ}C$ ) and  $V_{INA} = V_{INC} = V_{INC} = 5V$ , typical values are at  $T_A = +25^{\circ}C$ , unless otherwise specified.)

| SYMBOL                            | PARAMETER                             | CONDITIONS                                             | MIN                                                   | TYP                                                  | MAX   | UNIT  |

|-----------------------------------|---------------------------------------|--------------------------------------------------------|-------------------------------------------------------|------------------------------------------------------|-------|-------|

| Input Power Sup                   | ply                                   |                                                        |                                                       |                                                      |       |       |

| Vin                               | Input Supply Voltage DC Voltage       |                                                        | 4.25                                                  | 5                                                    | 5.5   | V     |

| Vina, Vinb, Vinc                  | Input supply Voltage VINA, VINB, VINC | V <sub>IN</sub> Rising                                 | 4.25                                                  | 5                                                    | 5.5   | v     |

| I <sub>Q_VIN</sub>                | VIN Supply Current                    | VR_EN=0; all LDO, SWA to SWC off, T <sub>A</sub> =25°C |                                                       |                                                      | 25    | μA    |

| SWA / SWB                         | ·                                     |                                                        |                                                       |                                                      |       | •     |

| Vout_swa/b                        | Output Voltage Setting                | Setting by reg_0x21[7:1]/<br>0x25[7:1]                 | 0.8                                                   | 1.1                                                  | 1.435 | V     |

| Vout_swa/b                        | Output Voltage Accuracy               | V <sub>BAT</sub> =5V only, I <sub>out</sub> =0, CCM    | -0.75                                                 |                                                      | 0.75  | %     |

|                                   | Dynamic Voltage Scale slew rate       |                                                        |                                                       | 1                                                    |       | mV/µs |

| So<br>So<br>Rds(on)_swa/swb_h Hig | Soft-start Time                       | t <sub>set</sub> = 1ms to 14 ms                        | -15                                                   |                                                      | 15    | %     |

|                                   | Soft-stop Time                        | t <sub>set</sub> = 0.5ms to 4 ms                       | -20                                                   |                                                      | 20    | %     |

| Rds(on)_swa/swb_h                 | High side MOSFET RDS(ON)              |                                                        |                                                       | 16                                                   |       | mΩ    |

| Rds(on)_swa/swb_l                 | Low side MOSFET RDS(ON)               |                                                        |                                                       | 10                                                   |       | mΩ    |

| ,                                 |                                       | Setting by reg_0x29[5:4]/<br>0x2A[5:4]=00 (default)    | -15%                                                  | 0.75                                                 | +15%  | MHz   |

|                                   |                                       | Setting by reg_0x29[5:4]/<br>0x2A[5:4]=01              | -15%                                                  | 1.0                                                  | +15%  | MHz   |

| fsw_swa/b                         | Switching Frequency                   | Setting by reg_0x29[5:4]/<br>0x2A[5:4]=10              | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | MHz                                                  |       |       |

|                                   |                                       | Setting by reg_0x29[5:4]/<br>0x2A[5:4]=11              | -15%                                                  | $\begin{array}{cccccccccccccccccccccccccccccccccccc$ | MHz   |       |

|                                   |                                       | Setting by reg_0x22[5:4]/<br>0x26[5:4]=00              | -15% 1.25 +15%<br>-15% 1.5 +15%                       | %                                                    |       |       |

|                                   |                                       | Setting by reg_0x22[5:4]/<br>0x26[5:4]=01              |                                                       | 10                                                   |       | %     |

|                                   | OVP Threshold                         | Setting by reg_0x22[5:4]/<br>0x26[5:4]=10 (default)    |                                                       | 12.5                                                 |       | %     |

|                                   |                                       | Setting by reg_0x22[5:4]/<br>0x26[5:4]=11              |                                                       | 20                                                   |       | %     |

| tovpdly_swa/b                     | OVP Propagation Delay                 |                                                        |                                                       | 5                                                    |       | μs    |

|                                   |                                       | Setting by reg_0x22[3:2]/<br>0x26[3:2]=00 (default)    |                                                       | -10                                                  |       | %     |

|                                   | UVP Threshold                         | Setting by reg_0x22[3:2]/<br>0x26[3:2]=01              |                                                       | -12.5                                                |       | %     |

## **Electrical Characteristics(Continued)**

Limits apply over the full operating ambient temperature range ( $0^{\circ}C \le T_A \le +85^{\circ}C$ ) and  $V_{INA} = V_{INC} = V_{INC} = 5V$ , typical values are at  $T_A = +25^{\circ}C$ , unless otherwise specified.)

| SYMBOL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | PARAMETER                                                | CONDITIONS                        | MIN                                                                                                                                                                                                                                                                                                           | TYP                                                                                                                                                                                                                                   | MAX    | UNIT  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------|--|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                          | Setting by reg_0x22[3:2]/         |                                                                                                                                                                                                                                                                                                               | 75                                                                                                                                                                                                                                    |        | 0/    |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | UVP Threshold                                            | 0x26[3:2]=10                      |                                                                                                                                                                                                                                                                                                               | -7.5                                                                                                                                                                                                                                  |        | %     |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | OVP Threshold                                            | Setting by reg_0x22[3:2]/         | $\begin{array}{c c} & 4.5 \\ & 5.0 \\ \hline \\ 1.5 & 1.8 \\ -0.75 \\ \hline \\ 1 \\ -15 \\ -20 \\ \hline \\ -20 \\ \hline \\ 50 \\ 40 \\ -15 \\ 0.75 \\ \hline \\ -15 \\ 0.75 \\ \hline \\ -15 \\ 1.0 \\ -15 \\ 1.25 \\ \hline \\ -15 \\ 1.5 \\ \hline \\ 1.5 \\ \hline \\ 1.25 \\ 20 \\ \hline \end{array}$ |                                                                                                                                                                                                                                       | 0/2    |       |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                          | 0x26[3:2]=11                      |                                                                                                                                                                                                                                                                                                               | -20         5         3.5         4.0         4.5         5.0         5.0         1.8         2.135         1         0.75         1         15         0.75         1         1.25         +15%         1.25         10         12.5 | 70     |       |  |

| t <sub>UVPDLY_</sub> SWA/B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | UVP Propagation Delay                                    |                                   |                                                                                                                                                                                                                                                                                                               | 5                                                                                                                                                                                                                                     |        | μs    |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                          | Valley current limited Setting by |                                                                                                                                                                                                                                                                                                               | 35                                                                                                                                                                                                                                    |        | Δ     |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                          | reg_0x20[7:6]/[3:2]=00            |                                                                                                                                                                                                                                                                                                               | 5.5                                                                                                                                                                                                                                   |        | ^     |  |

| ILIM_SWA/B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Current Limit                                            | Setting by reg_0x20[7:6]/[3:2]=01 |                                                                                                                                                                                                                                                                                                               | 4.0                                                                                                                                                                                                                                   |        | Α     |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | $\begin{tabular}{ c c c c c c c c c c c c c c c c c c c$ | Α                                 |                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                       |        |       |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                          | Setting by reg_0x20[7:6]/[3:2]=11 |                                                                                                                                                                                                                                                                                                               | 5.0                                                                                                                                                                                                                                   |        | ^     |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                          | (default)                         |                                                                                                                                                                                                                                                                                                               | 5.0                                                                                                                                                                                                                                   |        | ~     |  |

| SWC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                          |                                   |                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                       |        |       |  |

| V <sub>OUT_SWC</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Output Voltage Setting                                   |                                   | 1.5                                                                                                                                                                                                                                                                                                           | 1.8                                                                                                                                                                                                                                   | 2.135  | V     |  |

| Vout_swc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Output Voltage Accuracy                                  | I <sub>out</sub> = 0, CCM         | -0.75                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                       | 0.75   | %     |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Dynamic Voltage Scale slew rate                          |                                   |                                                                                                                                                                                                                                                                                                               | 1                                                                                                                                                                                                                                     |        | mV/µs |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Soft-start Time                                          | t <sub>set</sub> = 1ms to 14ms    | -15                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                       | 15     | %     |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Soft-stop Time                                           | t <sub>set</sub> = 0.5ms to 4ms   | -20                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                       | 20     | %     |  |

| Rds(on)_swc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | High side MOSFET RDS(ON)                                 |                                   |                                                                                                                                                                                                                                                                                                               | 50                                                                                                                                                                                                                                    |        | mΩ    |  |

| RDS(ON)_SWC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Low side MOSFET RDS(ON)                                  |                                   |                                                                                                                                                                                                                                                                                                               | 40                                                                                                                                                                                                                                    |        | mΩ    |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                          | Setting by reg_0x2A[1:0]=00       | 450/                                                                                                                                                                                                                                                                                                          | 0.75                                                                                                                                                                                                                                  | . 450/ |       |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                          | (default)                         | -15%                                                                                                                                                                                                                                                                                                          | 0.75                                                                                                                                                                                                                                  | +15%   |       |  |

| fsw_swc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Switching Frequency                                      | Setting by reg_0x2A[1:0]=01       | -15%                                                                                                                                                                                                                                                                                                          | 1.0                                                                                                                                                                                                                                   | +15%   | MHz   |  |

| ILIN_SWARE         Current Limit         reg_0x20[7:6]/[3:2]=00           Setting by reg_0x20[7:6]/[3:2]=10         4           Setting by reg_0x20[7:6]/[3:2]=10         4           Setting by reg_0x20[7:6]/[3:2]=10         4           Setting by reg_0x20[7:6]/[3:2]=10         4           Setting by reg_0x20[7:6]/[3:2]=11         5           SWC         Vour_swc         Output Voltage Setting         1.5           Vour_swc         Output Voltage Accuracy         Iout = 0, CCM         -0.75           Dynamic Voltage Scale slew rate         -         -         -           Soft-start Time         test = 1ms to 14ms         -15           Soft-stop Time         test = 0.5ms to 4ms         -20           Ros(on)_swc         High side MOSFET Ros(on)         -         -           Ros(on)_swc         Low side MOSFET Ros(on)         -         -           fsw_swc         Switching Frequency         Setting by reg_0x2A[1:0]=00         -15%         0.           fsw_swc         Switching Frequency         Setting by reg_0x2A[1:0]=10         -15%         1.           fsw_swc         Switching Frequency         Setting by reg_0x2A[1:0]=10         -15%         1.           fsw_swc         Switing by reg_0x2A[1:0]=01         -15% <td< td=""><td>1.25</td><td>+15%</td><td></td></td<> | 1.25                                                     | +15%                              |                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                       |        |       |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                          | Setting by reg_0x2A[1:0]=11       | $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                       |        |       |  |

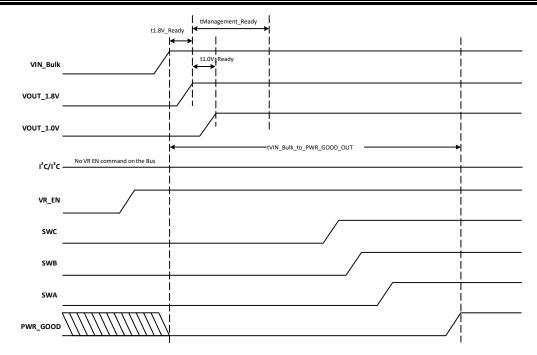

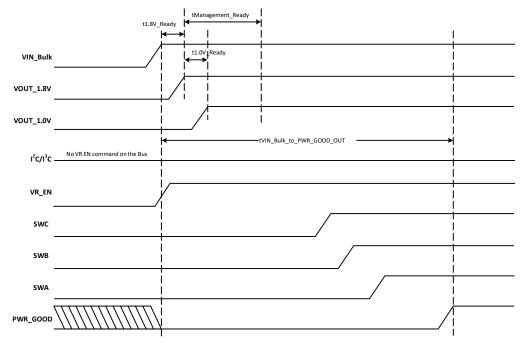

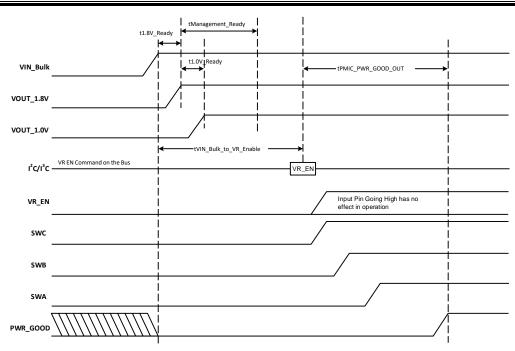

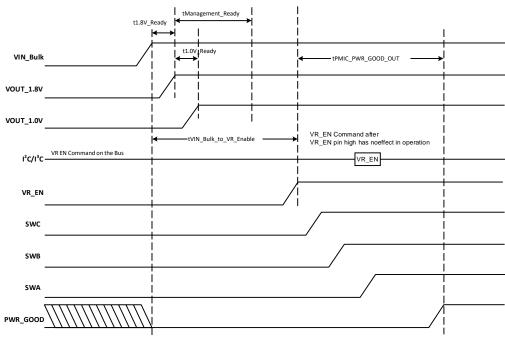

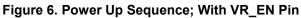

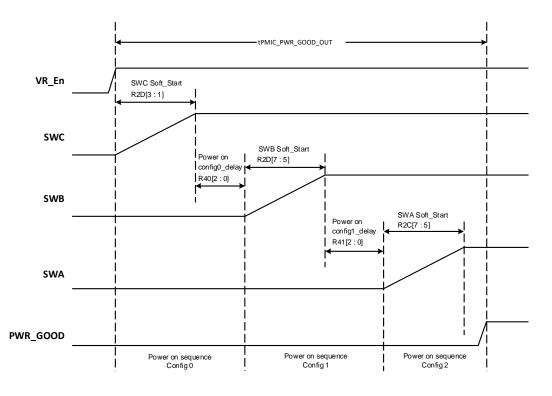

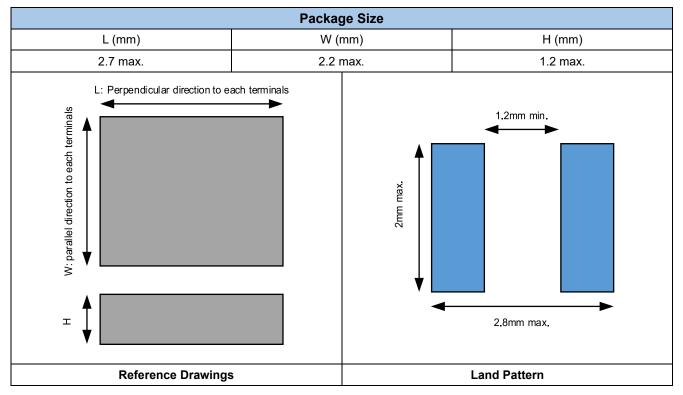

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                          | Setting by reg_0x28[5:4]=00       |                                                                                                                                                                                                                                                                                                               | 7.5                                                                                                                                                                                                                                   |        |       |  |